# High-Power Broad-Band AlGaN/GaN HEMT MMICs on SiC Substrates

Bruce M. Green, *Member, IEEE*, Vinayak Tilak, Sungjae Lee, *Student Member, IEEE*, Hyungtak Kim, *Student Member, IEEE*, Joseph A. Smart, Kevin J. Webb, *Senior Member, IEEE*, James R. Shealy, *Member, IEEE*, and Lester F. Eastman, *Life Fellow, IEEE*

**Abstract**—Broad-band high-power cascode AlGaN/GaN high electron-mobility transistor monolithic-microwave integrated-circuit (MMIC) amplifiers with high gain and power-added efficiency (PAE) have been fabricated on high-thermal conductivity SiC substrates. A cascode gain cell exhibiting 5 W of power at 8 GHz with a small-signal gain of 19 dB was realized. A nonuniform distributed amplifier (NDA) based on this process was designed, fabricated, and tested, yielding a saturated output power of 3–6 W over a dc–8-GHz bandwidth with an associated PAE of 13%–31%. A broad-band amplifier MMIC using cascode cells in conjunction with a lossy-match input matching network showed a useful operating range of dc–8 GHz with an output power of 5–7.5 W and a PAE of 20%–33% over this range. The third-order intermodulation products of the amplifiers under two-tone excitation were studied and third-order-intercept values of 42 and 43 dBm (computed using two-tone carrier power) for the lossy match and NDA amplifiers were obtained.

**Index Terms**—Broad-band amplifier, cascode, distributed amplifier, GaN, high electron-mobility transistor, silicon carbide.

## I. INTRODUCTION

FOR DECADES, the realization of broad-band high-power monolithic-microwave integrated-circuit (MMIC) power amplifiers has posed a significant challenge to microwave design and systems engineers due to the electrical and thermal limitations of GaAs transistor technology. In recent years, AlGaN/GaN high electron-mobility transistor (HEMT) technology has established itself as a strong contender for such applications because of its large electron velocity ( $>1 \times 10^7$  cm/s), bandgap (3.4 eV), breakdown voltage ( $>50$  V for  $f_T = 50$  GHz), and sheet carrier concentration ( $n_S > 1 \times 10^{13}$  cm $^{-2}$ ). Due to the superior electronic properties of the material and the possibility to grow the material on high thermal conductivity (3.5 W/cm · K) SiC substrates, power densities as high as 10.7 W/mm at 10 GHz [1] and 6.5 W/mm at 20 GHz [2] have been achieved.

Manuscript received March 30, 2001; revised August 24, 2001. This work was supported by the Office of Naval Research under Multidisciplinary University Research Initiative Contract N00014-96-1-1223 monitored by Dr. John Zolper.

B. M. Green was with the School of Electrical and Computer Engineering, Cornell University, Ithaca, NY 14853 USA. He is now with the Semiconductor Products Sector, DigitalDNA Laboratories, Motorola Inc., Tempe, AZ 85284 USA (e-mail: Bruce.M.Green@motorola.com.).

V. Tilak, H. Kim, J. R. Shealy, and L. F. Eastman are with the School of Electrical and Computer Engineering, Cornell University, Ithaca, NY 14853 USA.

S. Lee and K. J. Webb are with the School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN 47907 USA.

J. A. Smart is with RF Nitro Communications Inc., Charlotte, NC 28269 USA.

Publisher Item Identifier S 0018-9480(01)10438-2.

This paper addresses the problems associated with broad-band high-power MMIC power amplifiers on both the device technology and circuit design fronts by the use of high-performance AlGaN/GaN HEMTs in MMIC amplifier configurations optimized for high power and power-added efficiency (PAE). Previous work on GaN-based circuits has shown the viability of these devices for microwave circuit applications [3]–[7]. However, to date, no multioctave power-amplifier MMIC results using AlGaN/GaN HEMTs grown on high thermal-conductivity SiC substrates have appeared in the published literature. This paper describes the design and development of the first multioctave broad-band MMICs based on AlGaN/GaN HEMTs fabricated on high thermal-conductivity SiC substrates for simple efficient device heat sinking. First, technology used to fabricate the active and passive devices on SiC substrates is described. Next, the large-signal operation of the cascode power cell in terms of its dynamic loadline behavior is compared to the measured dc  $I$ – $V$  characteristics for the device, showing strong correlation of the dc and microwave current. Results for cascode pairs of 0.25- and 1-mm peripheries show excellent power scaling properties, as both devices realized output power densities of  $\geq 5$  W/mm ( $\geq 36\%$  PAE) at 8 GHz at a drain bias of 30 V. The design and characteristics of cascode broad-band power MMICs using both nonuniform distributed amplifier (NDA) and lossy-match designs are then given. In each case, a dc–8-GHz 3-dB bandwidth was achieved with output powers of 3–6 and 5–7.5 W and associated PAEs of 13%–31% and 20%–33%, respectively. Evaluation of the amplifiers under two-tone excitation yielded third-order intercept point (IP3) values of 43 and 42 dBm.

## II. GALLIUM–NITRIDE HEMT DEVICE AND CIRCUIT TECHNOLOGY

Multioctave high-power amplifiers demand microwave devices with high power density. Consider a uniform distributed amplifier (DA) with a cutoff frequency  $f_c$ , gate-line characteristic impedance  $Z_G$ , and maximum output power  $P_{\max}$  consisting of  $N$  sections and having transistors with a maximum output power  $P_o$  and gate–source capacitance  $C_{GS}$ . Its power bandwidth product (PBW) is defined by

$$\text{PBW} = f_c P_{\max}. \quad (1)$$

An upper bound on this quantity may be written as

$$\text{PBW} \leq \frac{NP_o}{\pi Z_G C_{GS}} = \frac{N(V_{\text{br}} - V_{\text{knee}})^2}{8\pi Z_D Z_G C_{GS}}. \quad (2)$$

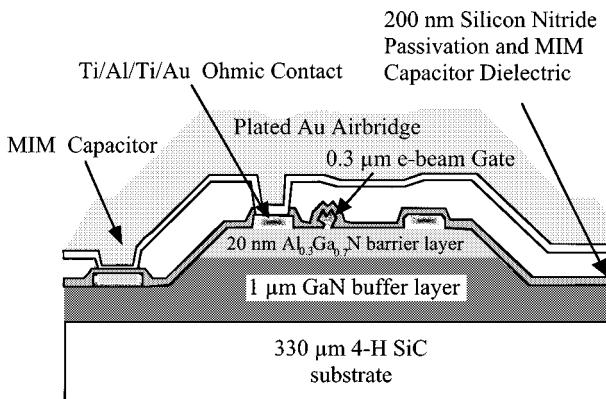

Fig. 1. Cross-sectional diagram showing the MMIC process for AlGaN/GaN HEMTs on SiC substrates.

where  $V_{knee}$  is the knee voltage of the transistor,  $V_{br}$  is its drain–source breakdown voltage, and  $Z_D$  is the load presented to its drain terminal. Clearly, for a fixed gate-line impedance  $Z_G$ , the watts per picofarad ratio  $P_0/C_{GS}$  dictates the PBW of the amplifier. For a given transistor technology,  $P_0/C_{GS}$  is a fixed quantity since according to (2),  $P_0$  depends on  $V_{br}$ , which, along with  $C_{GS}$ , increases with gate length. AlGaN/GaN HEMTs combine a frequency response similar to GaAs-based devices with significantly higher current densities and breakdown voltages. This enhancement in performance over GaAs on a watt-per-picofarad basis raises the output power obtainable from a wide-band amplifier. The following paragraphs describe the process and characteristics of AlGaN/GaN HEMTs and then discuss the large-signal scaling properties and dynamic loadline behavior of AlGaN/GaN HEMTs in a cascode configuration.

#### A. MMIC Process

A simple seven-mask-level MMIC process, depicted in Fig. 1, is used to fabricate the devices and circuits of this study. The wafers used to fabricate the MMICs are grown by organo–metallic vapor phase epitaxy and consist of a 50-nm AlGaN nucleation layer followed by a 1–1.5- $\mu$ m GaN buffer and Al<sub>0.3</sub>Ga<sub>0.7</sub>N barrier layers grown on 4-H SiC substrates. Alignment marks are formed with a Pt layer for both e-beam and optical alignments. Next, mesas for active transistors as well as resistors are etched to a depth of 220 nm using a Cl<sub>2</sub>-based electron–cyclotron resonance (ECR) etching tool. Ohmic contact to the two-dimensional electron gas is accomplished by the use of a Ti (20 nm)/Al (120 nm)/Ti (45 nm)/Au (55 nm) ohmic contact metal stack that is patterned using an e-beam liftoff process and then annealed in an 800 °C N<sub>2</sub> ambient for 30 s. Mushroom gates employing an Ni Schottky barrier are formed using direct e-beam writing in conjunction with a tri-level resist scheme. All devices have a gate length of 0.30  $\mu$ m. The first level interconnect metal is patterned using optical lithography and the liftoff technique. A 200-nm Si<sub>3</sub>N<sub>4</sub> passivation/dielectric layer is applied after the interconnect metal to passivate the high-field regions of the devices, as well as to form a dielectric for metal–insulator–metal (MIM) capacitors. Past studies [8] indicate that this passivation layer plays a role in helping to suppress long-time constant charge

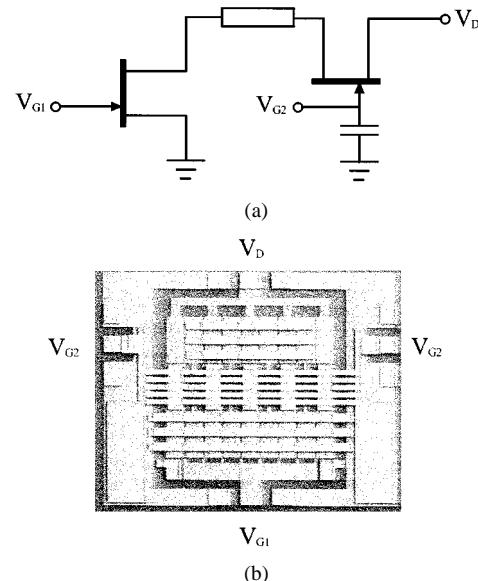

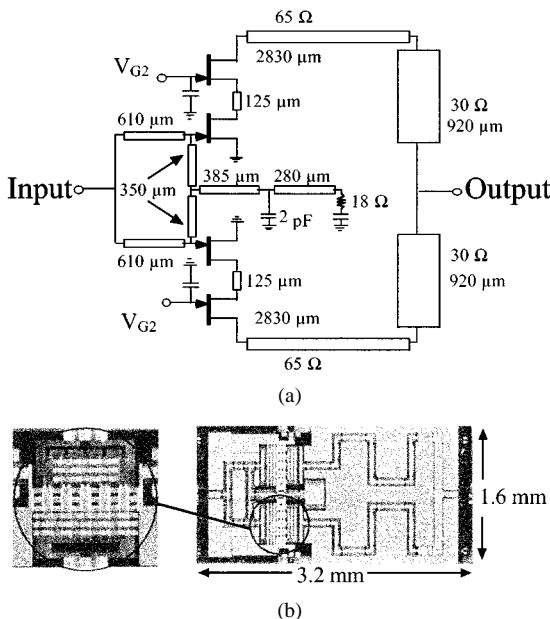

Fig. 2. (a) Circuit schematic and (b) SEM image of cascode cell with  $W_1 = W_2 = 1$  mm and  $\mu$ m and  $W_1 = W_2 = 0.25$  mm  $L_{G1} = L_{G2} = 0.3$   $\mu$ m. Die size  $0.7 \times 0.6$  mm<sup>2</sup>.

storage in surface states in the high field surface region of our undoped HEMT devices. Following the passivation step, holes are etched in the Si<sub>3</sub>N<sub>4</sub> using reactive ion etching to allow for contact to the first-level interconnect metal. Air bridges are then plated to a thickness of 2.5  $\mu$ m using a two-level optical resist and electroplating scheme.

Devices with gate peripheries of 150  $\mu$ m fabricated using this same process were recently measured at 10 GHz and yielded power densities of 10.7 W/mm when tuned for maximum power [1]. In this study, lower drain biases and, subsequently, lower power densities are used to ensure reliability of the devices and circuits over many power sweeps.

Since this process has no backside via-hole process developed, coplanar waveguide (CPW) technology is used for the creation of the transmission lines used in the MMICs. Using the electroplated Au deposited on top of the first level of evaporated Au to achieve a total thickness of 2.8  $\mu$ m, transmission lines with nominal impedances of 30, 50, 60, and 80  $\Omega$  and losses of 1–1.5 dB/mm are realized.

#### B. Dynamic Loadline and Power Scaling of Cascode-Connected Gallium–Nitride HEMTs

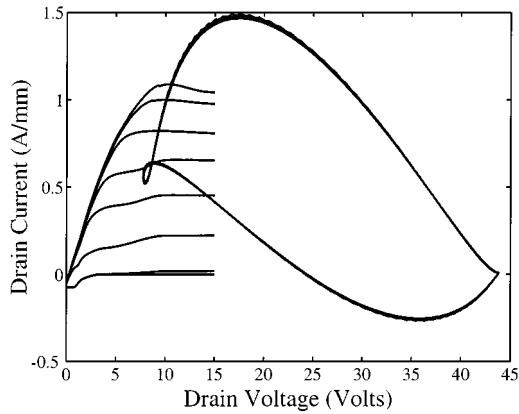

The circuits presented here use the cascode configuration shown in Fig. 2 due to the high gain associated with its low feedback capacitance and output conductance. In its early stages, AlGaN/GaN HEMT transistor technology suffered from electron trapping effects that decreased the current carrying capability of the devices in the high-field gate–drain region. This effect caused the microwave channel current and, hence, output power to be lower than that predicted by dc  $I$ – $V$  curves [8]. Fig. 3 compares the measured 8-GHz dynamic loadline behavior of a cascode-connected 0.3 × 250  $\mu$ m<sup>2</sup> device to its measured dc  $I$ – $V$  characteristics. As seen from the figure, trapping effects are minimal, as good correlation between the dc  $I$ – $V$  curves and the realized microwave current swing of 1 A/mm is evident. The dynamic loadline measurement was

Fig. 3. 8-GHz dynamic loadline and dc  $I$ - $V$  curves ( $V_{G1,\text{top}} = +1$  V,  $V_{G1,\text{step}} = -1$  V) for cascode cell with  $W_1 = W_2 = 250$   $\mu\text{m}$  and  $L_{G1,G2} = 0.3$   $\mu\text{m}$ . Bias:  $V_D = 25$  V,  $V_{G1} = -3$  V,  $V_{G2} = +5$  V.

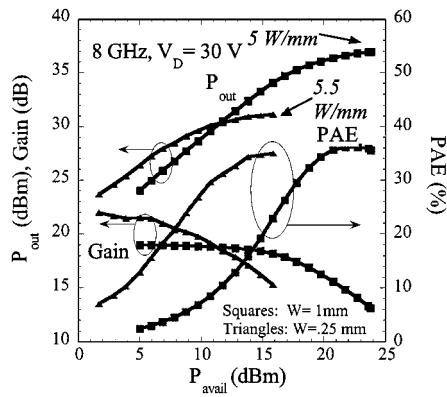

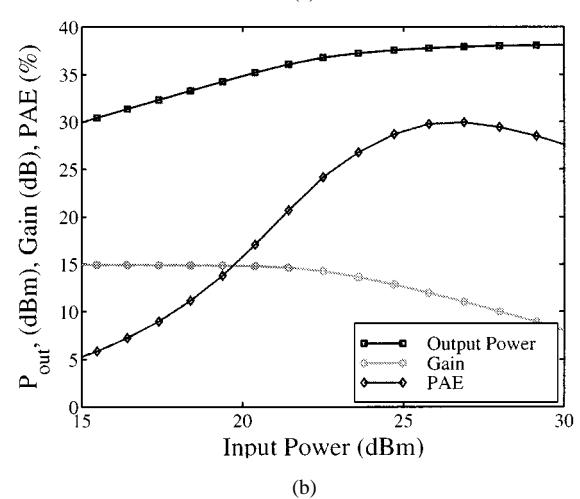

Fig. 4. Comparison of saturated output power, gain, and PAE as a function of input drive power for cascode cells with  $W_1 = W_2 = 1$  mm (Fig. 2) and  $W_1 = W_2 = 0.25$  mm ( $L_{G1} = L_{G2} = 0.3$   $\mu\text{m}$ ) under conditions of  $V_D = 30$  V,  $V_{G1} = -3$  V,  $V_{G2} = +5$  V, and a frequency of 8 GHz.

performed using a 4–26.5-GHz Maury load-pull system with HP 708208A microwave transition analyzers (MTAs) used in place of power meters [9]. The voltage swing and maximum channel current, as evidenced by the dynamic loadline, enables a power density of 4.5 W/mm to be obtained under bias conditions of  $V_D = 25$  V,  $V_{G1} = -3$  V, and  $V_{G2} = +5$  V.

Fig. 2(b) shows one of the two types of cascode cells used in the amplifier circuits of this paper. It contains 1 mm of total gate periphery for both the common source (CS) and common gate (CG) devices. This device uses a 125- $\mu\text{m}$  section of a high-impedance transmission line to separate the CS and CG devices. This separation allows the devices to have some degree of thermal isolation from one another, thus increasing the ability of the device to dissipate heat. Additionally, the series inductance provided by the high-impedance transmission line gives gain peaking. Fig. 4 demonstrates the excellent power scaling properties of this cascode pair due, in part, to the high thermal conductivity SiC substrate. The figure compares the output power density, gain, and PAE of a  $W_1 = W_2 = 0.250$ -mm device with that of a  $W_1 = W_2 = 1$ -mm device. In each case, a power density of 5 W/mm and a PAE of 36% was met or exceeded at a bias point of  $V_D = 30$  V,  $V_{G1} = -3$  V, and  $V_{G2} = +5$  V.

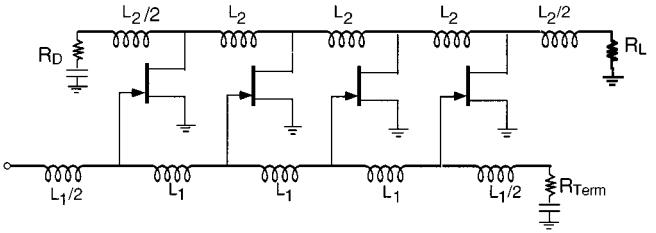

Fig. 5. Schematic of ideal uniform DA.

### III. NDA

DAs offer broad-band operation by incorporating gain elements in synthetic lumped-element approximate transmission lines, realized by the transistor capacitances and intervening inductances [10]. This topology allows the addition of transconductance  $g_m$  without adding device capacitance, thus resulting in excellent gain-bandwidth product. However, conventional DAs do not have good PAE because: 1) power is consumed by the synthetic drain-line termination dummy load; 2) the devices are loaded nonuniformly along the drain line; and 3) frequency-dependent attenuation along the gate line results in nonuniform drive of the active devices.

Quantitatively, the ratio of the power dissipated in the drain-line dummy load of Fig. 5,  $P_D$ , to the power dissipated in the output load  $P_L$  varies as the ratio of frequency to cutoff frequency  $f/f_c$  and number of transistors  $N$ . At frequencies well below the amplifier cutoff frequency  $f_c$ , this ratio, i.e.,  $P_D/P_L$ , is given as

$$\frac{P_D}{P_L} = \frac{\sin^2(2fN/f_c)}{N^2 \sin^2(2f/f_c)} \quad (3)$$

where

$$f_c = \frac{1}{\pi \sqrt{L_G C_{GS}}}. \quad (4)$$

Here,  $L_G$  refers to the inductance of the gate-line ladder network sections and  $C_{GS}$  refers to the gate-source capacitance. It is clear from this expression that near dc, the power dissipated in the dummy load is equal to that delivered in the external load. At frequencies above  $f_c\pi/2N$ ,  $P_D/P_L < -13$  dB. At higher frequencies, however, nonoptimum and nonuniform device loading degrades the realized output power and PAE [11]. In addition, frequency-dependent attenuation along the gate line causes nonuniform drive of each transistor [12]. The result of the nonuniform drive is premature compression of the transistor closest to the amplifier input and insufficient drive of the transistors closest to the gate-line termination resistor.

#### A. Design

Three cascode-connected AlGaN/GaN HEMT cells, having 0.3- $\mu\text{m}$  (each) gate lengths and 1-mm (each) gate peripheries, were employed to design and fabricate broad-band high-power MMIC NDAs. These cascode devices, optimized for a very compact layout, consist of adjacent CS and CG device gate fingers placed 6  $\mu\text{m}$  apart with a 4- $\mu\text{m}$  strip of ohmic contact metal between them, as described in [4]. Eight 125- $\mu\text{m}$ -long

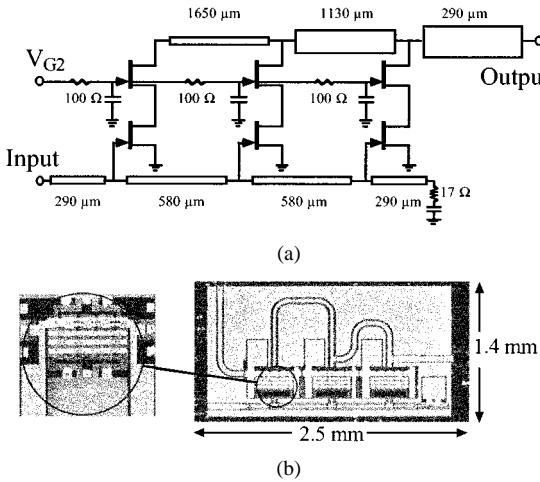

Fig. 6. (a) Circuit schematic and (b) chip photo of the NDA and detail of 1-mm cascode cell photograph. Die size:  $2.5 \times 1.4 \text{ mm}^2$ . All gate CPW line impedances are  $80 \Omega$ , and the drain-line impedances, from the left- to right-hand side, are 60, 50, and  $30 \Omega$ .

CS/CG finger pairs are placed in parallel to form an overall device with 1 mm of total gate periphery for both the CS and CG devices. A Curtice cubic nonlinear device model for the cascode cell used in the amplifier design was based on measurements of single-gate  $0.3 \times 250 \mu\text{m}^2$  periphery transistors [9].

Using the nonlinear transistor model, a uniform DA having a drain-line dummy load was designed initially to ensure the bandwidth (dc–8 GHz). The drain-line dummy load was then removed, and the gate- and drain-line sections were carefully optimized for optimum power and efficiency using the genetic algorithm (GA) method [13]. The schematic of the amplifier designed is shown in Fig. 6(a). The NDA inductances are realized using air-bridged CPW lines, as described in Section II-A, with the lengths indicated in Fig. 6(a). The circuit parameters, i.e., the gate and drain inductive line lengths, resulted from the iterative optimization. The optimization goals were specified so that the three-stage NDA has a flat gain and high efficiency throughout the band (dc–8 GHz). The photograph of the fabricated circuit is shown in Fig. 6(b). Note the absence of the drain-line dummy load and the varying CPW drain-line lengths between each of the three gain stages, indicative of the nonuniform inductance values. Also note that the lines nearer the output are of lower characteristic impedance and, hence, are wider and more able to supply higher dc current in class-A bias, to mitigate electromigration problems [14]. The corresponding center conductor widths of the CPW drain lines are 27, 40, and  $66 \mu\text{m}$ , with ground-to-ground spacing of  $80 \mu\text{m}$ .

### B. Experimental Results

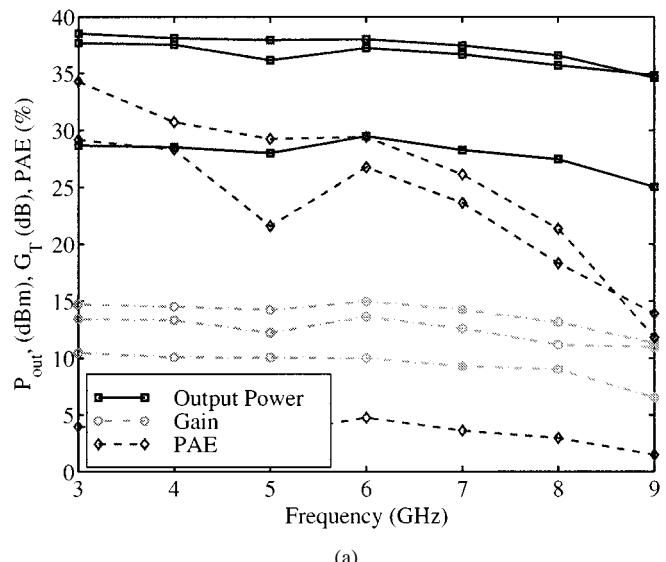

The measured small-signal  $|S_{21}|$  for the fabricated NDA in a  $25\Omega$  system showed a 3-dB bandwidth of dc–8 GHz with  $>13$ -dB small-signal gain, as seen in Fig. 7. On-wafer large-signal measurements yielded a continuous wave (CW) power of 3–6 W over 3–8 GHz and a maximum PAE of 31% with 6 W of associated output power at 3 GHz. These measurement results, shown in Fig. 8(a), were taken at  $P_{\text{in}}$  values of 10, 25, and 28 dBm, which correspond to linear gain  $P_{1\text{dB}}$  and  $P_{\text{sat}}$ . For

Fig. 7. Measured scattering parameters of an NDA of Fig. 6 under conditions of  $V_D = 15 \text{ V}$ ,  $V_{G1} = -4 \text{ V}$ ,  $V_{G2} = +5 \text{ V}$ .

Fig. 8. Measured large signal results for the cascode-connected HEMT NDA with  $25\Omega$  source and load impedances. (a) Power spectrum measured at small signal ( $P_{\text{in}} = 10 \text{ dBm}$ ),  $P_{1\text{dB}}$  ( $P_{\text{in}} = 25 \text{ dBm}$ ),  $P_{\text{sat}}$  ( $P_{\text{in}} = 28 \text{ dBm}$ ). (b) Power sweep at 5 GHz.

these measurements, the source and load impedance were set to  $25\Omega$  at each frequency using electromechanical tuners. The bias conditions for these measurements were  $V_D = 25 \text{ V}$ ,  $V_{G1} =$

Fig. 9. (a) Circuit diagram and (b) chip photograph of the lossy-match broad-band amplifier and detail of 1-mm inductively peaked cascode cell (cascode cell not drawn to scale). Input matching network transmission lines have impedance  $Z_0 = 80 \Omega$ .

$-3$  V, and  $V_{G2} = 5$  V (class-A operation). As shown in this figure,  $P_{\text{sat}}$  exceeds  $P_{1\text{dB}}$  by only 1.5 dB over the entire band of operation. With the same bias condition, the power sweep of Fig. 8(b) was measured at 5 GHz where a saturated output power of 5 W at 25% PAE was achieved.

#### IV. LOSSY-MATCH CASCODE POWER AMPLIFIER

The broad-band lossy match amplifier of Fig. 9 completely eliminates the traveling-wave structure for the addition of drain currents, but retains the constant  $k$  filter sections on the input to achieve flat gain. In this way, the devices can be driven to peak efficiency and their output power match is easily controlled. Also, unlike the NDA, this technique avoids the need to simultaneously optimize both the gain flatness and device loading.

##### A. Design

Two 1-mm cascode cells of Fig. 2 whose large-signal operation was described in Section II-B were used to realize lossy match wide-band amplifier. A wide-band amplifier was created by absorbing the capacitance on the input of the cascode into artificial transmission-line sections terminated by a resistor of value  $R_{\text{term}}$  according to the design technique depicted in Fig. 9(a). This broad-band design technique reduces the circuit's transducer gain at low frequencies to a value given by

$$G_T = \left( \frac{R_{\text{term}}^2}{R_{\text{term}} + Z_0} g_{m,\text{tot}} \right)^2 \quad (5)$$

where  $g_{m,\text{tot}}$  refers to the combined transconductances of the cascode devices and  $Z_0$  refers to the impedance of the input source ( $25 \Omega$ ). The cutoff frequency is approximated by (4)

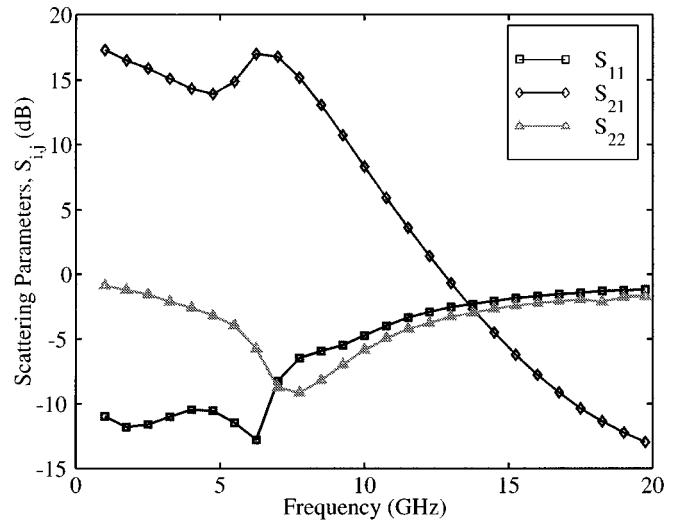

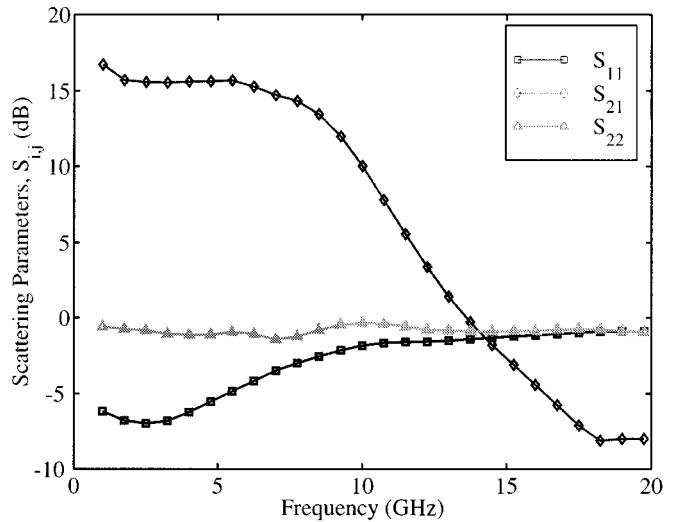

Fig. 10. Measured scattering parameters of cascode power amplifier of Fig. 9 under conditions of  $V_D = 15$  V,  $V_{G1} = -4$  V, and  $V_{G2} = +5$  V.

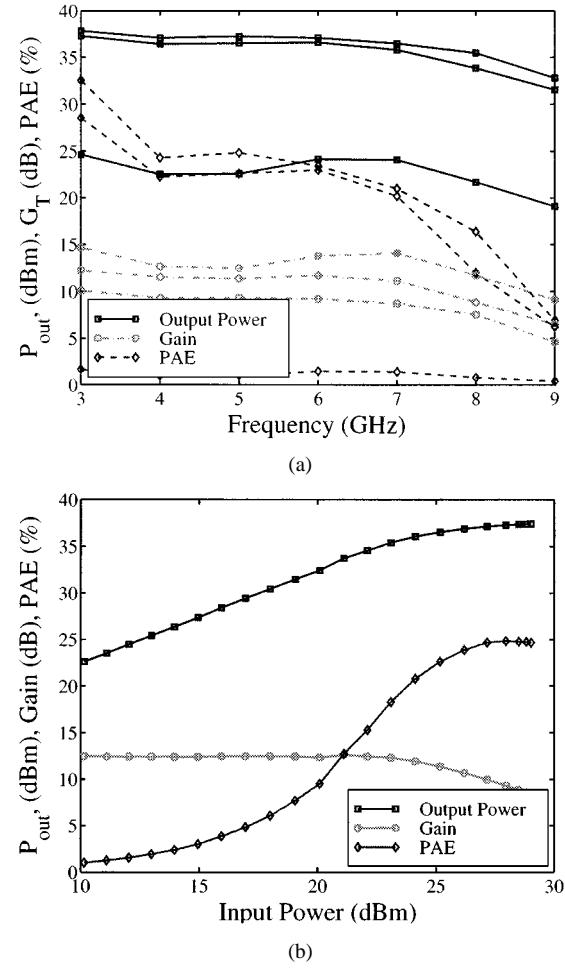

Fig. 11. Measured large-signal results for the lossy match amplifier with  $25\Omega$  source and load impedances. (a) Power spectrum measured at small signal ( $P_{\text{in}} = 14$  dBm),  $P_{1\text{dB}}$  ( $P_{\text{in}} = 24$  dBm),  $P_{\text{sat}}$  ( $P_{\text{in}} = 28$  dBm). (b) Power sweep at 6 GHz.

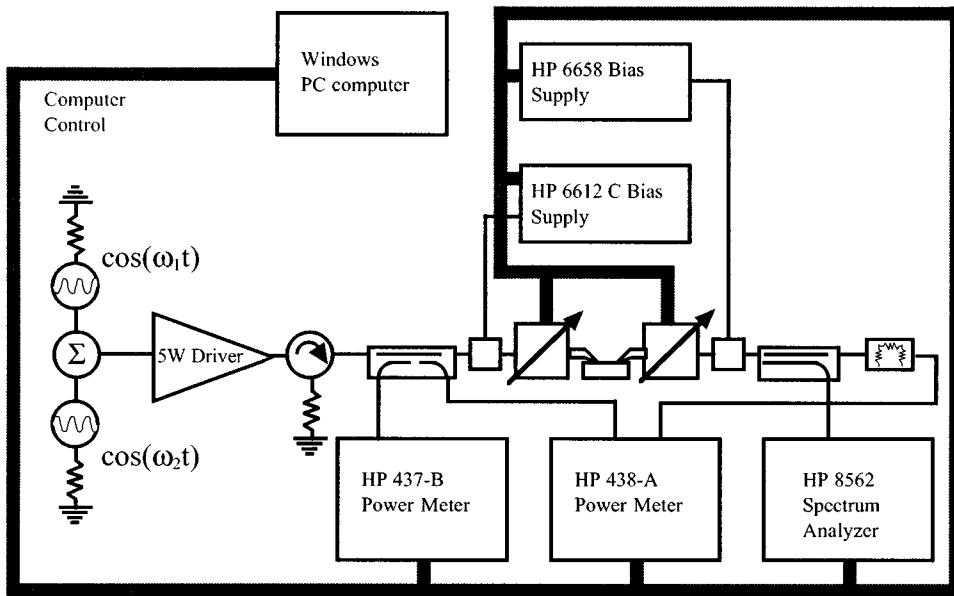

Fig. 12. Block diagram of two-tone power measurement system used to evaluate intermodulation products for the MMICs at 6 GHz.

where  $L_G$  and  $C_{GS}$  are defined by the cascode device's input capacitance and the additional constraint on the inductance given by

$$Z_0 = \sqrt{\frac{L_G}{C_{GS}}}. \quad (6)$$

The output matching sections of the amplifier are  $\pi$  sections, consisting of the shunt output capacitance of the cascode device in series with the series inductance and shunt capacitance provided by a 65 - to 30  $\Omega$  step in the transmission-line impedance. As with the NDA amplifier discussed above, a nonlinear Curtice cubic device model based on parameter extraction of the  $0.3 \times 250 \mu\text{m}^2$  device was used for the circuit design and optimization. Using the device model and these design guidelines, the amplifier was designed and fabricated. Fig. 9(b) shows a photograph of the finished amplifier.

### B. Experimental Results

Measured scattering parameters for the amplifier in Fig. 10 show the flat gain achieved by the design that provides a 3-dB bandwidth of 8 GHz. While this amplifier maintains less ripple in the forward gain than the NDA of Section III,  $|S_{11}|$  is 3 dB higher than that of the NDA. As seen in Fig. 11(a), on-wafer power measurements using a load-pull system, with the input and output impedances to the circuit set to  $25 \Omega$  and constant input powers of 14 dBm (small signal), 24 dBm ( $P_{1\text{dB}}$ ), and 29 dBm ( $P_{\text{sat}}$ ), resulted in a saturated output power of 5–7.5 W over a 3–8-GHz frequency range. The achieved PAEs are 20%–33% over this range. Fig. 11(b) shows the saturation characteristics of the power amplifier measured at 6 GHz, where a small-signal gain of 15 dB, an output power of 6.3 W, and a PAE of 30% were obtained. From both of these figures, it can be seen that  $P_{\text{sat}}$  and  $P_{1\text{dB}}$  vary by only 1 dB and the PAE improves only marginally beyond  $P_{1\text{dB}}$ . This behavior is indicative of reasonably good linearity properties of the

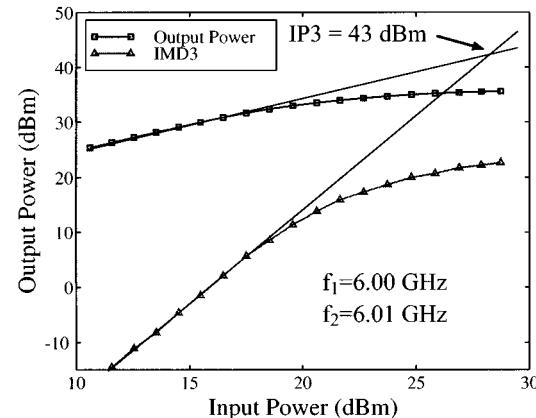

Fig. 13. Saturation characteristics of the NDA of Fig. 6 under two-tone excitation ( $f_1 = 6$  GHz,  $f_2 = 6.01$  GHz). Bias:  $V_D = 25$  V,  $V_{G1} = -3$  V,  $V_{G2} = +5$  V.

cascode devices. The bias point of the amplifier for all of these data was  $V_D = 25$  V,  $V_{G1} = -3$  V, and  $V_{G2} = 5$  V.

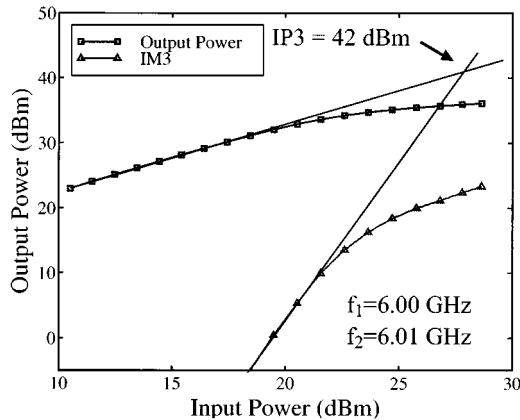

### V. INTERMODULATION-DISTORTION CHARACTERISTICS

Using the measurement system of Fig. 12, 6-GHz two-tone measurements were performed to characterize the intermodulation products of the amplifiers discussed in Sections III and IV. Fig. 13 shows the intermodulation characteristics for the NDA of Fig. 6, while Fig. 14 shows the intermodulation characteristics for the lossy match amplifier of Fig. 9. The IP3 is determined by extrapolating the portion of the saturation characteristics in which the amplifier nonlinearity does not impact the amplifier gain significantly. For the NDA of Fig. 6, an IP3 of 43 dBm was obtained at a bias point of  $V_D = 25$  V,  $V_{G1} = -3$  V, and  $V_{G2} = +5$  V. At the same bias point and frequency, the lossy match amplifier of Fig. 9 achieved a IP3 of 42 dBm. These IP3 results, along with single-tone large-signal results, are summarized in Table I.

TABLE I

COMPARISON OF LARGE-SIGNAL CHARACTERISTICS FOR NDA AND LOSSY MATCH AMPLIFIER

| Design | Die Area<br>(mm <sup>2</sup> ) | BW<br>(W-GHz) | $P_{sat}$<br>(dBm) | $P_{1dB}$<br>(dBm) | Pwr. Dens.<br>(W/mm) | PAE<br>(%) | $IP3$ (2-tn.)<br>(dBm) | $P_{1dB,2-tone}$<br>(dBm) |

|--------|--------------------------------|---------------|--------------------|--------------------|----------------------|------------|------------------------|---------------------------|

| LMCC   | 5.1                            | DC - 8        | 38.0               | 37.0               | 3.2                  | 30         | 42                     | 34.2                      |

| NDA    | 3.5                            | DC - 8        | 37.1               | 35.7               | 1.7                  | 23         | 43                     | 32.3                      |

Fig. 14. Saturation characteristics of lossy-match amplifier of Fig. 9 under two-tone excitation ( $f_1 = 6$  GHz,  $f_2 = 6.01$  GHz). Bias:  $V_D = 25$  V,  $V_{G1} = -3$  V,  $V_{G2} = +5$  V.

Care must be used in interpreting the IP3 data of the amplifiers. In the case of the NDA,  $IP3 - P_{1dB,2tone} = 10.3$  dB. For the lossy-match amplifier,  $IP3 - P_{1dB,2tone} = 7.8$  dB. A standard power series analysis [15] shows that a difference of 9.6 dB is expected between IP3 and the *single-tone*  $P_{1dB}$ . A comparison of the  $P_{1dB}$  levels under two-tone excitation (shown in Figs. 13 and 14) shows that the  $P_{1dB}$  levels under two-tone conditions is approximately 2 dB lower than the  $P_{1dB}$  levels under single-tone excitation shown in Figs. 8 and 14. Therefore, the value of IP3 taken on the basis of comparing third-order intermodulation (IM3) with the single-tone output power is approximately 2 dB higher than that obtained by comparison with the two-tone output power shown in these figures.

## VI. DISCUSSION AND CONCLUSION

An AlGaN/GaN MMIC technology and realization of multi octave power amplifiers have been presented. The large-signal performance of cascode power cells shows the excellent electrical and thermal properties of the devices, resulting in high output power and excellent power scaling properties. State-of-the-art multi octave power performance was obtained using the cascode configuration in both NDA and lossy match broad-band power-amplifier designs. It is seen that, while the NDA provided better input and output matches, higher power and efficiency for a smaller total gate periphery (2 mm compared to 3 mm) could be obtained from the lossy match amplifier. To the authors' knowledge, the power levels achieved with these amplifiers are among the highest ever reported for multi octave MMICs. In comparison, a 2-W (pulsed) output power has been reported for a 2–8-GHz GaAs cascode heterojunction bipolar transistor (HBT) MMIC

DA ( $Z_{in} = Z_{out} = 50 \Omega$ ) [16]. It should be emphasized that the measured CW power results presented in this paper were achieved on-wafer and that with improved heat sinking or pulsed RF measurements, higher power levels may be possible. The measured IP3s for the amplifiers were respectable for a technology in its early stages. It is noteworthy that during repeated power sweeps, no significant degradation in the gain and PAE of the MMICs was observed. In any case, the results of this paper demonstrate the desirability of AlGaN/GaN HEMT MMIC technology for wide-band power amplification.

## ACKNOWLEDGMENT

The authors would like to acknowledge the staff of the Cornell Nanofabrication Facility, Cornell University, Ithaca, NY, for advice and assistance given in the fabrication of the MMICs, and A. Lindbom, Chalmers Institute of Technology, Göteborg, Sweden, for her assistance in programming the MTA for dynamic loadline analysis.

## REFERENCES

- [1] V. Tilak, B. Green, H. Kim, J. Smart, V. Kaper, T. Prunty, J. R. Shealy, and L. F. Eastman, "The influence of barrier thickness on the high power performance of AlGaN/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 22, pp. 504–506, Nov. 2001.

- [2] J. S. Moon, M. Micovic, P. Janke, P. Hashimoto, W.-S. Wong, R. D. Widman, L. McCray, A. Kurdoghlian, and C. Nguyen, "GaN/AlGaN HEMT's operating at 20 GHz with continuous-wave power density <6 W/mm," *Elect. Lett.*, vol. 37, no. 8, pp. 528–530, Apr. 2001.

- [3] J. J. Xu, S. Keller, G. Parish, S. Heikman, U. K. Mishra, and R. A. York, "A 3–10-GHz GaN-based flip-chip integrated broad-band power amplifier," *IEEE Trans. Microwave Theory Tech.*, vol. 48, pp. 2573–2578, Dec. 2000.

- [4] B. M. Green, K. K. Chu, V. Tilak, J. A. Smart, J. R. Shealy, and L. F. Eastman, "Cascode connected AlGaN/GaN HEMT's on SiC substrates," *IEEE Microwave Guided Wave Lett.*, vol. 10, pp. 316–318, Aug. 2000.

- [5] B. M. Green, S. Lee, K. Chu, K. J. Webb, and L. F. Eastman, "High-efficiency gallium nitride monolithic distributed amplifier," *IEEE Microwave Guided Wave Lett.*, vol. 10, pp. 270–272, July 2000.

- [6] K. Krishnamurthy, R. Vetary, S. Keller, U. Mishra, M. J. W. Rodwell, and S. I. Long, "Broadband GaAs MESFET and GaN HEMT resistive feedback power amplifiers," *IEEE J. Solid-State Circuits*, vol. 35, pp. 1285–1292, Sept. 2000.

- [7] S. T. Sheppard, W. L. Pribble, D. T. Emerson, Z. Ring, R. P. Smith, S. T. Allen, J. W. Milligan, and J. W. Palmour, "AlGaN/GaN HEMT MMIC development," in *Cornell High-Performance Devices Conf.*, Ithaca, NY, Aug. 2000, pp. 232–236.

- [8] B. M. Green, K. K. Chu, E. M. Chumbes, J. A. Smart, J. R. Shealy, and L. F. Eastman, "The role of surface passivation on the microwave characteristics of AlGaN/GaN HEMTs," *IEEE Electron Device Lett.*, vol. 21, pp. 268–270, June 2000.

- [9] B. M. Green, K. K. Chu, H. Kim, V. Tilak, J. A. Smart, J. R. Shealy, and L. F. Eastman, "Validation of a large signal model for AlGaN/GaN HEMTs," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Boston, MA, 2000, pp. 761–764.

- [10] E. L. Ginzton, W. R. Hewlett, J. H. Jasberg, and J. D. Noe, "Distributed amplification," *Proc. IRE*, vol. 36, pp. 956–969, Aug. 1948.

- [11] M. Campovecchio, B. Le Bras, R. Hilal, M. Lajugie, and J. Obregon, "Large signal design method of distributed power amplifiers applied to a 2–18 GHz GaAs chip exhibiting high power density performances," *Int. J. Microwave Millimeter-Wave Computer-Aided Eng.*, vol. 6, no. 4, pp. 259–269, 1996.

- [12] Y. Ayasli, R. L. Mozzi, J. L. Vorhaus, L. D. Reynolds, and R. A. Pucel, "A monolithic GaAs 1–13 GHz traveling-wave amplifier," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-30, pp. 967–981, 1982.

- [13] *Series IV, Simulating and Testing*, Agilent EEs of High-Frequency Design Solutions, Westlake Village, CA, 1995.

- [14] J. B. Beyer, S. N. Prasad, R. C. Becker, J. E. Nordman, and G. K. Hohenwarter, "MESFET distributed amplifier design guidelines," *IEEE Trans. Microwave Theory Tech.*, vol. MTT-32, pp. 268–275, Mar. 1984.

- [15] S. C. Cripps, *RF Power Amplifier Design*. Norwood, MA: Artech House, 1999.

- [16] J. P. Fraysse, J. P. Viaud, M. Campovecchio, P. Auxemery, and R. Quere, "A 2-W high-efficiency 2–8-GHz cascode HBT MMIC power distributed amplifier," in *IEEE MTT-S Int. Microwave Symp. Dig.*, Boston, MA, June 2000, pp. 529–532.

- [17] B. M. Green, K. K. Chu, V. Tilak, J. A. Smart, J. R. Shealy, and L. F. Eastman, "Cascode connected AlGaN/GaN HEMT's on SiC substrates," *IEEE Microwave Guided Wave Lett.*, vol. 10, pp. 316–318, Aug. 2000.

**Bruce M. Green** (S'96–M'01) received the B.S. and M.S. degrees from Brigham Young University (BYU), Provo, UT, in 1996 and 1997, respectively, and the Ph.D. degree from Cornell University, Ithaca, NY, in 2001.

In 2001, he joined the Digital DNA Laboratories, Motorola Inc., Tempe, AZ, where he performs research and development in the area of GaAs devices for wireless applications. He has authored or co-authored ten technical publications and has one patent pending. While with BYU, his research focused on

modeling the performance of personal communications antennas systems in indoor propagation environments. His research at Cornell University focused on the characteristics and design of gallium-nitride devices and integrated circuits for high-power high-frequency applications.

Dr. Green is a member of Tau Beta Pi and Eta Kappa Nu. He was the recipient of the 1996 National Science Foundation Graduate Research Fellowship, the 1998 IEEE Microwave Theory and Techniques Society (IEEE MTT-S) Graduate Fellowship, and the 1999 Schlumberger Foundation Fellowship.

**Vinayak Tilak** was born in Chennai, India, in 1974. He received the B.S. degree in electrical engineering and the M.S. in physics from the Birla Institute of Technology and Science, Pilani, India, and is currently working toward the Ph.D. degree in applied physics at Cornell University, Ithaca, NY.

His research interests include design, fabrication, and modeling of GaN devices.

**Sungjae Lee** (S'98) received the B.S. degree in electrical engineering from the Seoul National University, Seoul, Korea, in 1998, the M.S. degree in electrical and computer engineering from Purdue University, West Lafayette, IN, in 2000, and is currently working toward the Ph.D. degree at Purdue University.

His research interests are broad-band power-amplifier design and noise characterization and modeling of AlGaN/GaN HEMTs.

Mr. Lee is a member of Eta Kappa Nu.

**Hyungtak Kim** (S'99) was born in Seoul, Korea, in 1973. He received the B.S. degree in electrical engineering from the Seoul National University, Seoul, Korea, in 1996, and is currently working toward the Ph.D. degree in electrical and computer engineering at Cornell University, Ithaca, NY.

He completed his military service in 1998. He is currently with the School of Electrical and Computer Engineering, Cornell University. His research interests include GaN-based devices and circuits for high-power and high-frequency applications.

**Joseph A. Smart** received the B.S.E.E. degree from the State University of New York, Binghamton, in 1987, the M.S. degree in materials science from Cornell University, Ithaca, NY, and is currently working toward the Ph.D. degree at Cornell University.

He spent seven years in industry involved with Si and GaAs technologies. His research work has been concentrated on GaAs and GaN epitaxial structures for electronic applications. He currently manages the Advanced Technology Group, RF Nitro Communications Inc., Charlotte, NC, for GAN-based HFETs. He has several patents filed for novel epitaxial growth techniques

**Kevin J. Webb** (S'81–M'84–SM'98) received the B.Eng. and M.Eng. degrees from the Royal Melbourne Institute of Technology, Melbourne, Australia, in 1978 and 1983, respectively, the M.S.E.E. degree from the University of California at Santa Barbara, in 1981, and the Ph.D. degree from the University of Illinois at Urbana-Champaign, in 1984.

He is currently a Professor at the School of Electrical and Computer Engineering, Purdue University, West Lafayette, IN.

**James R. Shealy** (M'97) received the B.S. degree from North Carolina State University, Raleigh, in 1978, the M.S. degree from Rensselaer Polytechnic Institute, Troy, NY, in 1980, and the Ph.D. degree from Cornell University, Ithaca, NY, in 1983.

He then held a dual appointment at Cornell University as a Research Associate and at General Electric as a Principal Staff Scientist. In 1987, he joined the Cornell University faculty, and was promoted to Full Professor in 1998. He is currently the Director of the OMVPE Facility and of the Optoelectronics Technology Center, Cornell University. He is also a member of the graduate faculty of Electrical Engineering and Materials Science. His current research focuses on GaN materials for power electronics.

Dr. Shealy founded and has chaired the Biennial International Workshop on OMVPE in 1983. He has been recognized for excellence in undergraduate teaching, and was the recipient of five awards for contributions to the curriculum in electrical engineering.

**Lester F. Eastman** (A'53–M'58–SM'65–F'69–LF'94) has been the John L. Given Foundation Chair Professor of Engineering at Cornell University, Ithaca, NY, since January 1985. He currently devotes full-time to graduate research. He has supervised over 100 Ph.D. doctoral students. In 1957, he joined the faculty of Electrical Engineering at Cornell University, and also serves as member of the graduate fields of applied physics and materials science. Since 1965, he has performed research on compound semiconductor materials, high-speed devices, and circuits, and has been active in organizing workshops and conferences on these subjects elsewhere since 1965 and at Cornell since 1967. In 1977, he joined other Cornell faculty members in obtaining funding and founded the National Research and Resource Facility for Submicron Structures at Cornell (now the Cornell Nanofabrication Facility). Also in 1977, he founded the Joint Services Electronics Program and served as the Program Director until 1987. In his research group, effort is underway on molecular-beam epitaxy, microwave transistors, high-speed semiconductor lasers, high-frequency photo-receivers, and fundamental phenomena in compound semiconductor, quantum, electron, and optical devices. From 1978 to 1979, he was on leave at the MIT Lincoln Laboratory, Lexington, MA. From 1985 to 1986, he was with the IBM Watson Research Laboratory. He has served as a consultant for several industries.

Dr. Eastman is a Fellow of the IEEE. He is a member of the National Academy of Engineering. He is the chairman of the Advisory Committee for the Materials Science Research Center of Excellence at Howard University, Washington, DC. During 1983, he was the IEEE Electron Device Society National Lecturer. He was a member of the U.S. Government Advisory Group on Electron Devices from 1978 to 1988. From 1987 to 1993, he served as a member of the Kuratorium (Visiting Senior Advisory Board) of the Fraunhofer Applied Physics Institute, Freiburg, Germany. In September 1991, he was the recipient of the GaAs Symposium Award, and the Heinrich Welker Medal. He was also the recipient of the 1994 Alexander von Humboldt Senior Fellowship and the 1995 Aldert van der Ziel Award. The IEEE has also honored him with the 1999 Graduate Teaching Award and he also received the 2000 Wisdom Award of Honor and the 2000 Centennial Medal of the IEEE.